テクノロジー

Rapidusが挑む2nm半導体とは

その技術的革新を解説

現代社会を支える半導体と、その進化の最前線

半導体はデジタル社会の基盤として、より高速かつ大容量の処理を目指して進化し続けています。そして半導体技術の進歩をけん引してきた鍵が「回路の微細化」、すなわちひとつのチップのトランジスタを小さくして、集積できる数を増やすことです。最先端技術では、半導体の微細化はついに2nm(ナノメートル)世代に突入しつつあります。

半導体プロセスルールとは何?なぜ微細化が重要なのか

半導体における「プロセスルール」とは、半導体を製造するプロセスの世代を示す指標で、nm単位で表現されます。例えば「○nmプロセス」という数値が小さいほど微細な加工技術を意味し、より細かい線幅で回路を描けることを示しています。かつてはこの数値がトランジスタのゲート長、すなわち最小加工寸法を直接表していましたが、近年は構造の進化に伴い物理寸法と一致しないケースが増えています。現在は「おおむね各世代で0.7倍ずつ縮小する」というスケーリングの目安として、○nmといった数値がプロセス世代の名称に使われるようになっています。

プロセスルールの微細化は半導体の性能向上や高集積化、コスト削減、低消費電力化に大きく寄与します。トランジスタが小さくなると電子の移動距離が短くなり、スイッチングが高速化して性能が向上します。チップに搭載できるトランジスタが増えれば、新たな機能を追加できます。一枚のウェーハからとれるチップの数が増えれば、製造コストが下がります。さらに、微細化によりスイッチングに必要な電荷量が減り、消費電力が削減されて電力効率が改善します。これはバッテリー駆動機器や大規模データセンターの省エネに直結する重要な効果です。

このように、プロセスルールの微細化は半導体の「性能」「集積度(機能)」「コスト」「電力効率」のすべてを向上させる鍵となってきました。そのため各社は競って微細化技術の研究開発を進め、ムーアの法則に沿う形で、およそ2年に一度のペースでプロセス世代を進めてきたのです。

半導体微細化の歴史と、立ちはだかる物理的な壁

1965年、のちにIntelの共同創業者となるGordon Moore(ゴードン・ムーア)氏は、「半導体集積回路に搭載される(トランジスタなどの)素子数は18〜24カ月で2倍になる」と提唱しました(ムーアの法則)。この法則は半導体の微細化(集積度向上)とコスト低下をもたらし、電子機器の高性能化と普及を半世紀以上にわたってけん引してきました。技術的限界は繰り返し指摘されましたが、新技術で毎回乗り越えてきました。

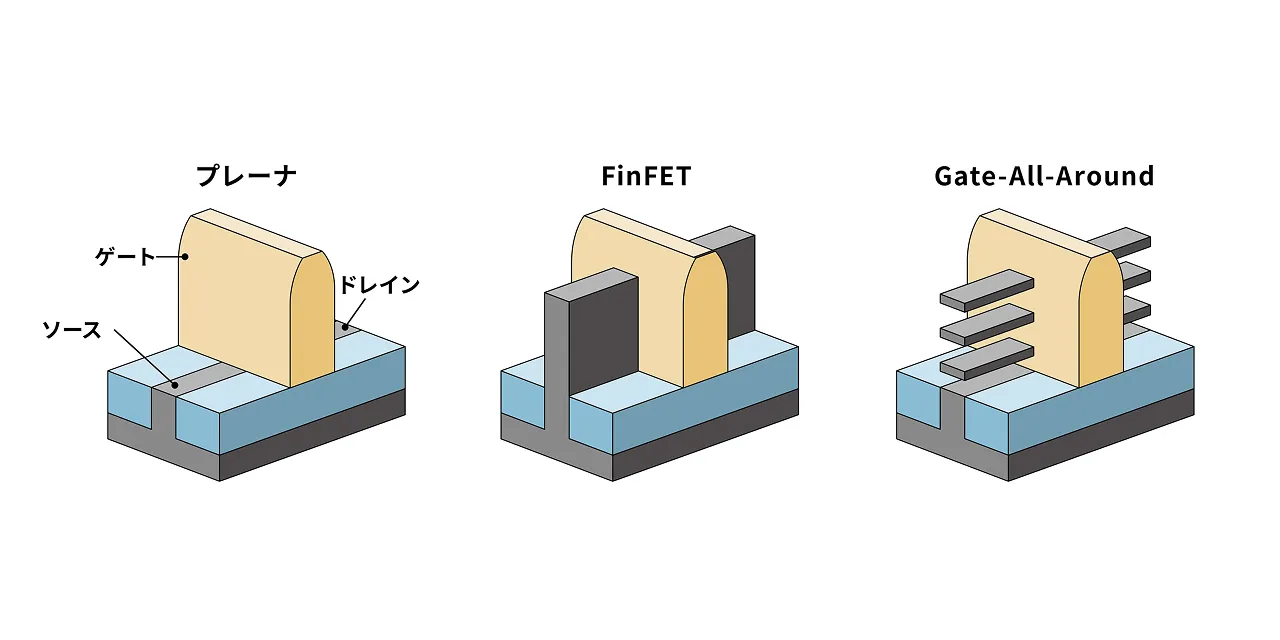

微細化の過程では、従来の「プレーナ型トランジスタ」のプロセスルールが20nm世代になるとリーク電流が増大し、スイッチオフ時に電流が流れる問題が顕著になりました。これを突破したのが2010年代前半に実用化された「FinFET」です。FinFETはチャネルを立体的な"フィン"構造とし、ゲートで3方向から囲むことでリーク電流を効果的に抑制しました。

露光技術は、波長193nmのArFエキシマレーザーでは10nm台のパターン形成が困難でした。そこで液浸露光や、一つのパターン形成に露光を2回以上行うマルチパターニング技術によって延命を図った後に、EUV露光技術が実用化されます。EUVにより10nm以下のパターン形成(いわゆる7nm世代以降)が実現しました。

今後は微細化の追求に加えて新しいトランジスタ構造や材料の開発とともに、チップを重ねる3D実装やチップレットなど、「ポスト・ムーア時代」を見据えた技術革新が活発に進んでいます。

極限への挑戦 2nmプロセスの「すごさ」とは

2nm世代の半導体技術は、7nmや5nm世代と比べて飛躍的な性能向上と省電力化を実現します。IBMが2021年に発表した2nm試作チップのデータによれば、同じ電力で動作させた場合は、7nm世代比で45%の性能向上、もしくは同じ性能なら75%もの消費電力削減が可能とされています。

従来のFinFETは概ね3nm世代までの微細化を支えてきましたが、3nm世代以降ではFinFETであってもリーク電流増加が大きな課題となります。

そこで登場したのがGAA(Gate-All-Around)構造のトランジスタです。GAAでは、チャネル部分をナノシートやナノワイヤ状に形成し、ゲート電極が全周囲からチャネルを取り囲む構造となっています。これにより電流制御性がさらに向上し、リーク電流を抑制してトランジスタのさらなる微細化と高性能化が両立できます。IBMの2nm試作チップも3層のシリコン・ナノシートを積み重ねたGAA構造を採用し、FinFETを超える性能と省電力性を実現しました。

2nmプロセスはAIやIoT需要に応える基盤技術としても注目されています。AIモデルの学習・推論には膨大な計算処理が必要であり、演算性能と電力効率を極限まで高めた半導体チップが求められます。2nm世代のチップはその高性能、省電力性により、サーバ向けのAIプロセッサやエッジデバイス向けのAIチップで威力を発揮します。IoT時代には無数の小型デバイスでAIやセンシングが行われますが、2nm世代クラスの省電力チップであれば電池駆動デバイスでも高度なAI機能を実装しやすくなります。

ただし、2nm世代の量産には技術的な課題も多く、製造ばらつきや歩留りの確保が難しくなっています。EUV露光など高額設備が必要なため、量産できる企業は世界で数社です。それでも2nmプロセスは、AIやデジタル社会の進化を支える"最先端の土台"として、今後の半導体産業をリードしていくことは間違いありません。

| 比較項目 | 4nm | 3nm | 2nm |

|---|---|---|---|

| 導入時期 | 2021~2022年 | 2022~2023年 | 2025年ごろ本格量産(予定) |

| トランジスタ構造 | FinFET | FinFET(一部企業はGAA) | GAA |

| トランジスタ密度(目安) | 約1.7億個/mm2 | 約2.5億個/mm2 | 約3億個/mm2以上 |

| 性能向上 | - | - | 同等面積で最大15~20%高速 |

| 電力効率 | 約10~15%削減(5nm比) | 約25%削減(5nm比) | 最大30~40%削減(3nm比) |

| 量産難易度 | 中~高(EUV導入初期) | 高い(EUV+FinFET) | 非常に高い(EUV+GAA) |

世界最先端への挑戦──Rapidusの2nmのロードマップ

現在、最先端のロジック半導体領域ではTSMC(台湾)、Samsung(韓国)、Intel(米国)といったグローバル企業が激しい開発競争を繰り広げています。Rapidusは、トヨタ、ソニー、NTTなど国内大手8社の協力と経済産業省の支援を受け、2022年の設立時に「2020年代後半に国内で2nmチップ量産」という目標を掲げました。

RapidusはIBM(米国)と共同で2nm世代技術の量産化を進めており、計150人のエンジニアをニューヨーク州アルバニーに送り込み最先端プロセスを習得。2025年4月には北海道千歳市に建設のIIM-1内にパイロットラインを立ち上げ、同年後半には試作サンプルの提供、2027年の量産開始を目指しています。日本発の最先端ファウンドリとして世界に新たな選択肢を提示します。

すでにTenstorrent(米国)と協業し、エッジ向けAIプロセッサIPの共同開発を開始しています。海外大手半導体ベンダーからもRapidusの2nm世代技術への関心が高まっています。同時に、IBM、imec(ベルギー)をはじめ装置・材料メーカーと幅広く連携し、北海道を中心に国内先端エコシステムを構築中です。

Rapidusは、確かな技術とパートナーシップを武器に、世界の最前線で輝く「日本発のファウンドリ」を実現します。

まとめ

現代デジタル社会の基盤を支える半導体は、より高速かつ大容量の処理を目指して進化を続けています。その進化の鍵を握るのが「回路の微細化」、すなわち「プロセスルール」の縮小です。最先端技術はついに2nm世代に突入しつつあり、IBMが2021年に発表した2nm試作チップのデータによれば、7nm世代比で45%の性能向上、または75%もの消費電力削減が可能とされています。この飛躍的な進化を支えるのが、GAA構造のトランジスタです。さらなる微細化と高性能化を両立させます。

日本国内では、Rapidusが2027年の2nmチップ量産開始を目指しています。RapidusはIBMとの共同開発を進めて世界に新たな選択肢を提示し、AIやIoT時代を支える最先端半導体の供給に貢献します。

トランジスタの一種で、従来の平面的なトランジスタ構造(プレーナ型)を立体的に改良したものです。FinFETは、プレーナ型とは異なり、チャネル部分を基板から垂直に突き出したフィン状に形成して、ゲートが3方向(上と両側面)から挟み込むような構造をしています。魚のひれ(fin)のような形状をしていることから、この名前が付けられました。FinFETは、微細化に伴うリーク電流の問題を解決し、性能向上と低消費電力化を実現するために開発されました。

半導体製造において、回路パターンをシリコンウェーハ上に転写する最先端の技術。2nmや3nmプロセスといった超微細な半導体の製造に不可欠です。半導体製造におけるリソグラフィ(露光)は、写真の現像のように、光に反応する材料(フォトレジスト)を塗布したウェーハに、回路パターンが描かれた「フォトマスク」を通して光を照射し、パターンを転写する技術です。EUVリソグラフィは、この工程で「極端紫外線」という特殊な光を使用します。

従来の露光技術(DUV:

Deep

Ultraviolet)は、波長が193nm程度の紫外線が使われていました。より微細な回路パターンを形成するためには、さらに短い波長の光が必要です。EUVリソグラフィは、波長13.5nmという極めて短い極端紫外線を使用してこれまで不可能だった超微細なパターン形成を可能にしました。

- #半導体

- #前工程

- #トランジスタ

- #GAA

- #歩留まり