テクノロジー

半導体設計はなぜ難しいのか

Rapidusが挑む“超高速”ものづくりの舞台裏

半導体設計とは

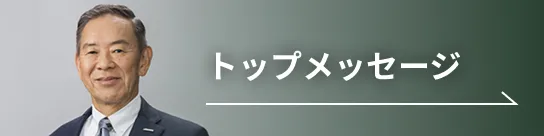

仕様定義からバックエンドまでの長い道のり

半導体設計は、最終製品に求められる機能の仕様定義から始まり回路設計(論理設計)、検証、物理設計(レイアウト)、そしてバックエンド設計へと続く長いプロセスを経て進行します。

まず、求められる機能や性能を仕様として明確化し、それを基にRTL(Register Transfer Level:レジスタ転送レベル)設計や論理合成で回路の動作を具体化します。次にシミュレーションや検証で論理の正しさを確認し、物理設計の段階ではトランジスタや配線パターンをレイアウトします。バックエンド工程は、タイミングや消費電力、製造上の制約を考慮しながら最終的なマスクデータを作成します。

各段階で多くの検証と最適化が必要で、設計から製造可能なデータに仕上げるまでには多くの専門知識と労力が求められます。

EDA、IPライブラリ、PDK:設計効率と製造適合を一気に高める“三種の神器”

半導体設計の効率化と製造適合性を劇的に高める“三種の神器”が、EDA(Electronic Design Automation)、IPライブラリ、PDK(Process Design Kit)です。

EDAは回路設計から検証、レイアウト、最終データ生成までの設計工程を自動化し、設計ミスの低減と開発期間の短縮を実現します。IPライブラリは、使用実績がある回路ブロックを部品のように再利用することで設計品質の向上と工数削減に寄与します。PDKは製造プロセスに最適化された設計ルールやシミュレーションモデル、標準セル情報などを提供し、設計と製造の橋渡し役を担います。

EDAの自動化パワー、IPの再利用性、PDKの製造準拠の3者の連携によって設計効率と製造適合性を飛躍的に向上させられるため、最先端半導体開発の基盤となっています。

半導体設計の難しさ

トランジスタ10億個時代がもたらす設計の激変

スマートフォンやPCなどに搭載される最新の半導体チップは、ムーアの法則に従って指数関数的に増加してきました。数cm角の半導体1チップの中には、今や数十億から数百億個ものトランジスタが集積されています。こうした半導体チップを設計する現代の半導体設計は極めて複雑化しているのです。膨大なトランジスタを正確に動作させるためには、論理設計やタイミング設計において高い難易度をクリアする必要があり、設計者の負担が増大しています。

高機能化や低消費電力化への要求が厳しくなり、消費電力や発熱、リーク電流など、さまざまな課題にも対応しなければなりません。設計生産性の向上も限界に近づいており、設計にかかる時間が長期化する傾向にあります。このような背景から、半導体設計は従来以上に高度な技術と効率化が求められる難しい分野となっています。

設計段階から作りやすさを織り込むDFMとOPC

DFM(Design For Manufacturing:製造容易性設計)とは、設計段階から製造プロセスで発生する可能性がある問題を予測し、歩留まりや信頼性の向上を目指すための設計手法です。微細化が進み、nm(ナノメートル)オーダーの加工精度が求められる現代の半導体製造は、パターンが設計通りにウェーハ上に転写されにくくなり、製造装置のばらつきや露光時の物理的限界によって「ホットスポット」と呼ばれる欠陥リスクが増加します。

OPC(Optical Proximity Correction:光近接効果補正)は、設計パターンと実際の転写パターンのズレを補正するために、マスクデータを事前に調整する技術です。

しかし、OPCだけでは装置のばらつきや複雑なレイアウトによる問題を全て解決できません。そこでDFMは、ホットスポットが発生しにくいパターンを設計段階で選別、修正して製造プロセス全体での歩留まり悪化を未然に防ぐ役割を担います。

設計段階から製造プロセスを考慮して半導体チップの品質や歩留まり、生産効率を最大化する手法やアプローチを意識しなければならないのです。

設計と製造を同時に最適化するRapidusの挑戦

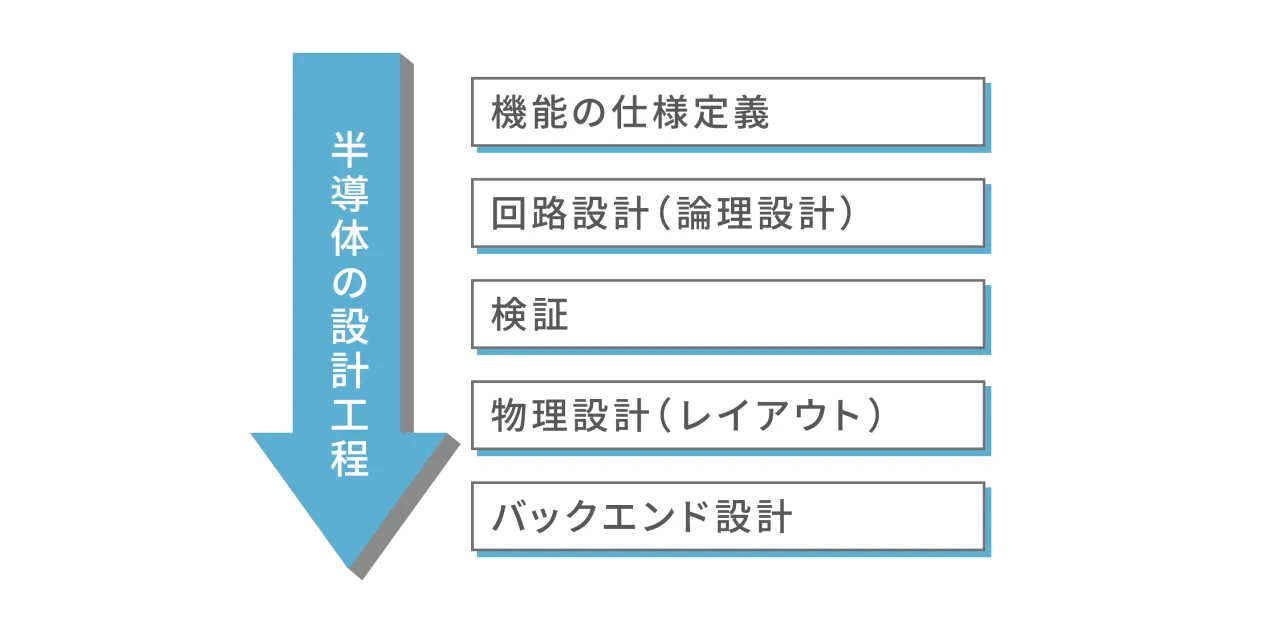

MFDとDMCO:“作りやすさ”から“設計しやすい工場”へ

このように複雑化している半導体設計において、効率化のためのさまざまな取り組みが進められています。Rapidusが着目している考え方が、MFD(Manufacturing For Design:設計のための製造)です。従来の“作りやすい設計”から“設計しやすい工場”への転換を目指す戦略です。

MFDはAIやセンサーを活用して製造工程から得られる膨大なデータを設計プロセスにフィードバックする仕組みです。これによって設計段階から製造現場の実データを反映でき、プロセスマージンや設計マージンを広げることが可能になります。

Rapidusが提唱するDMCO(Design-Manufacturing Co-Optimization)は、MFDとDFMを組み合わせた考え方です。DMCOは設計と製造を同時に最適化し、2nm世代の最先端半導体のような「次世代技術」において設計と製造プロセスの密接な連携を実現します。設計と製造の相互作用を反復的に評価・調整することで、製品の性能向上や高歩留まり、コスト削減を同時に達成させようとする試みです。

AI基盤Raadsが設計期間を劇的に短縮

RapidusのAI基盤であるRaads(Rapidus AI-Assisted Design Solutions)は、AIや機械学習技術を活用した独自の設計支援ツールです。Raadsは、従来のスタンダードセル設計を基盤としつつ、AIが設計の最適化プロセスを支援することで設計期間を劇的に短縮します。

自然言語で記述した仕様から製造用マスクパターンまで幅広い設計工程をカバーし、設計の効率化と最適化を同時に実現します。

AI活用によって設計から製造までの期間が短縮されることで、2nm世代のチップ設計も対応可能となります。Raadsの究極の狙いは、設計者の誰もが先端ノードを設計できる環境を整えて国内の半導体エコシステム全体を底上げすることにあります。

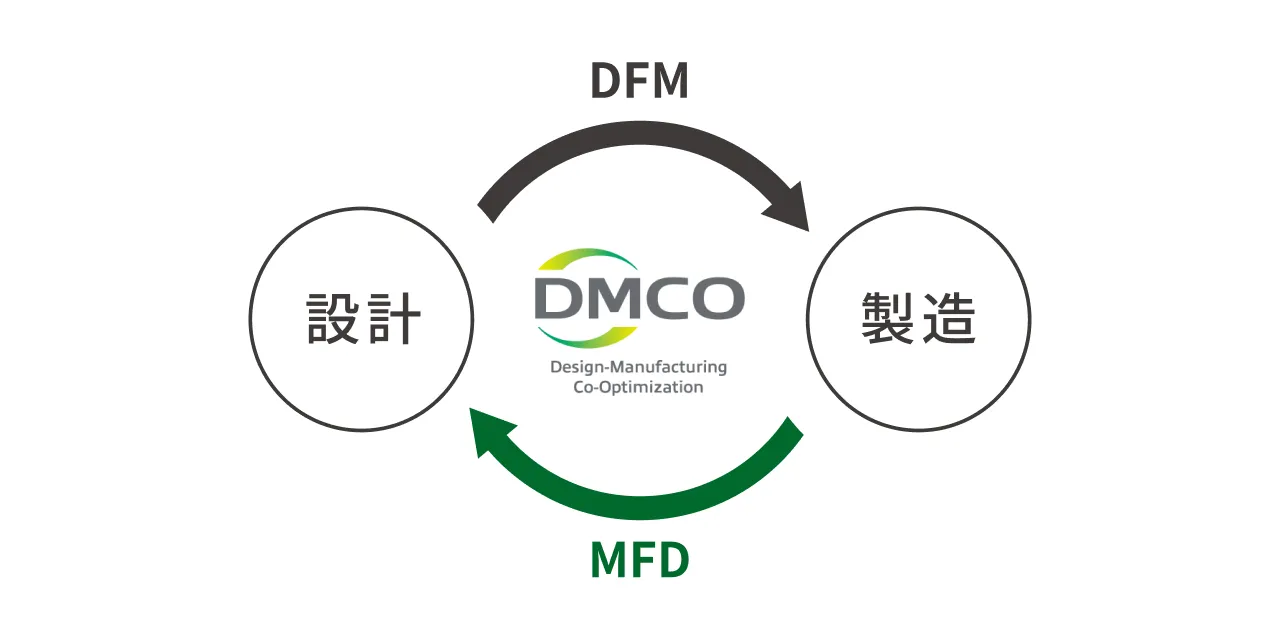

RapidusのRUMS構想

RapidusのRUMS(Rapid and Unified Manufacturing Service)構想は、半導体の設計支援から前工程であるウェーハ製造、後工程のパッケージングまで一貫して提供する新しいビジネスモデルです。

水平分業体制では分かれている各工程を統合してRapidusが一気通貫で担うことで、2nm世代プロセスやチップレットといった最先端技術を用いた半導体チップを、世界最速のサイクルタイムで提供します。

RUMSのコンセプトは「Integrative Co-Creation」(一体型共創)です。"設計も製造もRapid(迅速)に"というRapidusの社名のごとく、世界最短のトータル・サイクルタイムの実現に向けて取り組みを加速させます。

半導体集積回路(IC)を設計する際に必要な設計情報ファイルをまとめたもの。トランジスタやその他の素子のモデル、設計ルール、シミュレーションツール、レイアウトツール、検証ツールなどが含まれます。半導体製造を請け負うファウンドリから、ICを設計する企業(デザインハウス)などに提供されます。

電気信号の増幅やスイッチングを担う半導体素子のこと。現代のICはMOS(Metal-Oxide-Semiconductor)型が主流です。金属(ゲート)、酸化膜(絶縁層)、半導体(シリコン基板)の三層構造を持ち、ゲート、ソース、ドレインの三端子で構成されます。ゲートに電圧を加えることで酸化膜越しに電界が生じ、基板内部のキャリア分布が変化します。「n型MOS」では、ゲートに正電圧を印加するとチャンネル(反転層)が形成され、ソースからドレインへの電子の流れ、すなわち電流が流れるようになります。

MOSトランジスタのn型(NMOS)とp型(PMOS)を組み合わせたCMOSがICの基本構成となっています。このMOSトランジスタの微細化と高集積化の進展を予測したのがムーアの法則です。MOSトランジスタの構造と動作原理のシンプルさと微細化への適性が、ムーアの法則の実現を支えてきたのです。

- #半導体

- #設計

- #設計支援