テクノロジー

次世代半導体製造の鍵を握る「チップレット」とは

次世代半導体の需要が高まる中、従来の製造手法だけでは解決できない新たな技術的課題が顕在化しています。

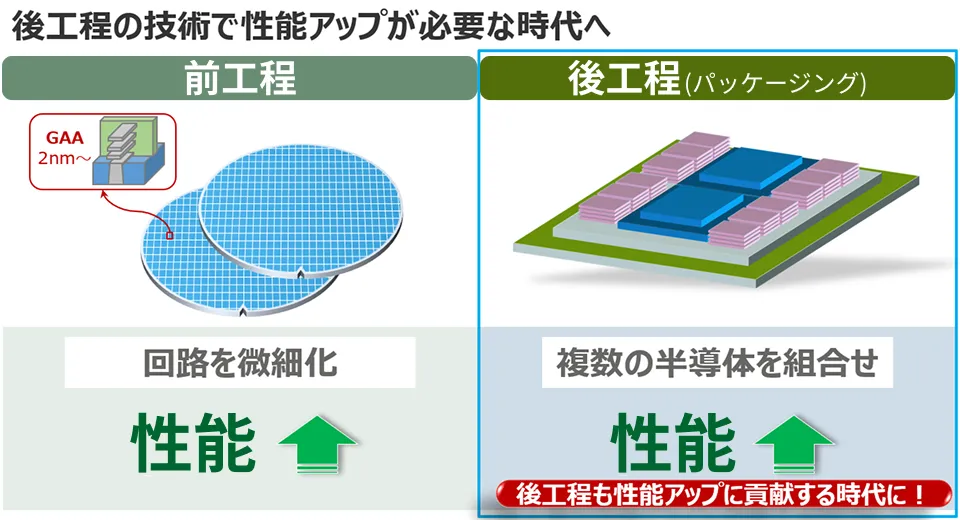

ムーアの法則の限界?半導体業界の課題と解決策

Intel共同創業者のゴードン・ムーア氏が1965年に提唱した「ムーアの法則」は、半世紀以上にわたって集積回路の性能向上とコスト低減をけん引し、現代のデジタル技術発展の基盤となりました。ムーアの法則とは、半導体チップが搭載するトランジスタなどの素子数は約2年ごとに倍増するというものです。

これまで長期間にわたって法則通りに技術開発が進んできました。しかし近年は回路線幅の微細化が数nm(ナノメートル)レベルに達し、物理的な限界や製造プロセスの複雑化、コストの上昇といった課題に直面しています。回路を小さくするほど、歩留まり(良品率)が下がりやすくなります。加えて、半導体工場を建設して運営するには多額の費用と高度な専門知識が不可欠です。これらの理由から「ムーアの法則を単純に続けていくことは難しい」という見方が広がっています。

こうした現状を打開する新たなアプローチとして注目されているのが「チップレット」です。

チップレットがもたらす新たな半導体設計

チップレットとは、大規模な一つのチップに含まれていた機能ブロックを小さなチップ(ダイ)に個片化したもので、複数のチップレットを単一のパッケージに集積(チップレット集積)して動作させます。

半導体製造は大規模な回路を1枚のウェーハに全て集積する方式が一般的でした。そのため不良箇所が一部でも見つかればチップ全体を廃棄しなければなりませんでした。チップレット集積であれば、あらかじめ良品のチップ(KGD:Known Good Die)だけを使用することにより歩留まりを著しく向上できます。

異なる回路を自由に組み合わせるヘテロジニアスインテグレーション

「ヘテロジニアスインテグレーション」とは、製造プロセスや機能が異なるダイを一つのパッケージに収める技術の総称です。チップレット集積は異種回路を組み合わせる上で特に効果的な手段の一つと言えます。最先端のプロセス性能が求められる計算回路は最新の半導体技術で製造し、メモリーやアナログ回路などは一世代前の技術を用いることでコストを抑えながら機能を充実させることができます。

この技術は自動車産業を中心に注目されています。複数の大手自動車メーカーが車載用SoC(System on Chip)の開発に取り入れており、量産車への2030年以降の搭載を目指しています。異種回路の組み合わせによって車載半導体の高性能化や多機能化を推し進めて、AI演算能力やグラフィック性能をより効率的に向上させると同時に製造時の歩留まり改善にもつながる点が大きなポイントです。

また、高い安全性が求められる自動車部品は「機能安全部品」といわれ、旧世代の成熟した信頼性の高いレガシー半導体が採用されるのが一般的です。しかし最新の予防安全装置「ADAS(正式名称)」や自動運転車、「SDV」(Software Defined Vehicle)などは、レガシー半導体だけでは性能要求を満たせません。ここで必要とされるのがチップレットの技術です。機能安全部品を制御するマイコンや大容量のメモリー、自動運転を可能にする高性能AI半導体を組み合わせるなど、メーカーの要求に合わせてSoCを短期間でカスタマイズできる点も、自動車業界が導入を積極的に検討している理由の一つです。

こうした利点は自動車以外にもAIや通信など多彩な領域へ波及し、あらゆる分野の技術革新を促す要因となっています。チップレットは、今後の半導体産業を支える重要なキーテクノロジーとして注目を集める存在になりつつあります。

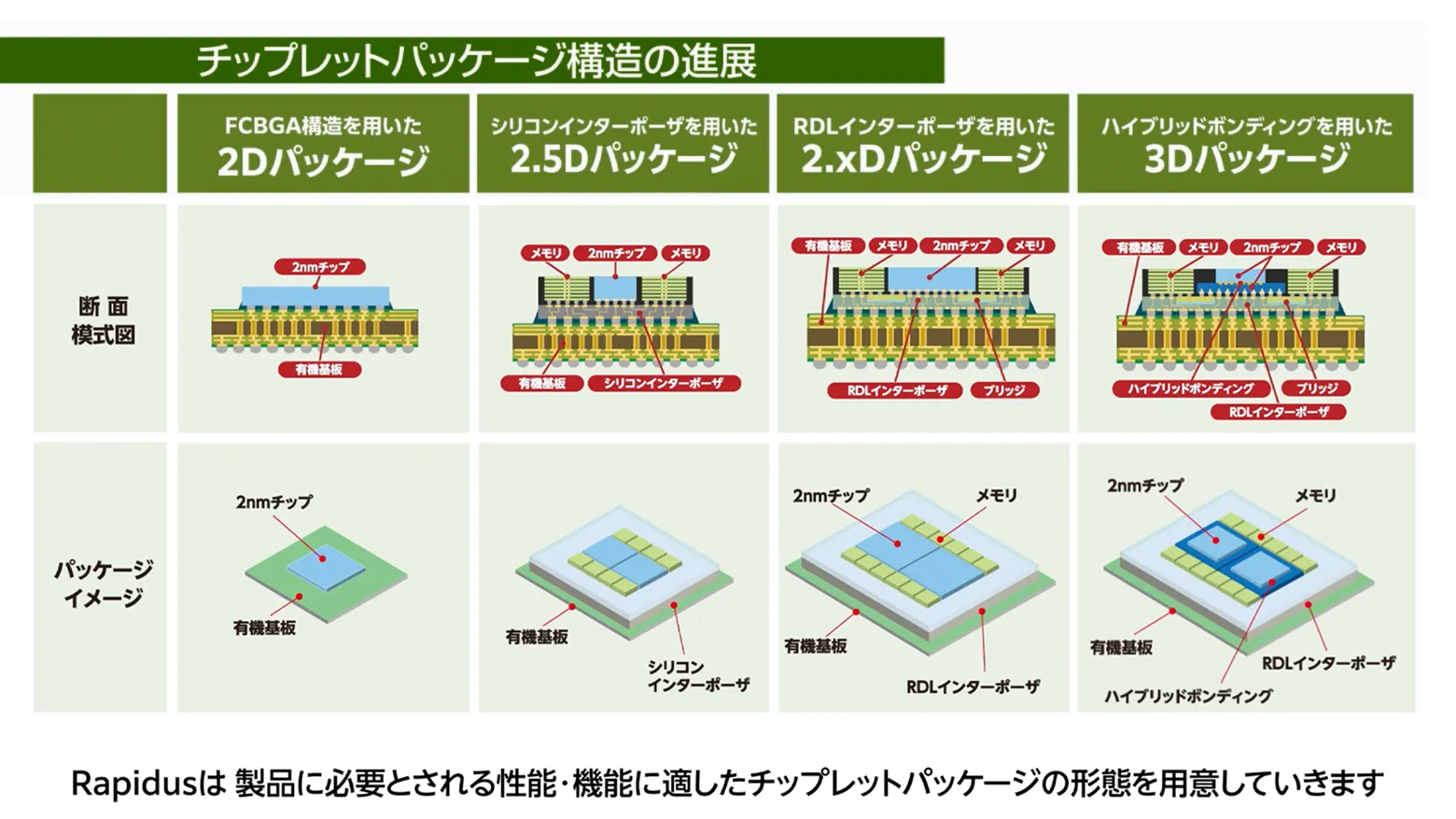

複数チップを一つにまとめるインターポーザの役割とは

チップレット集積には、複数のチップを高密度かつ高速に接続する技術が欠かせません。その要となるのが「インターポーザ」です。インターポーザは複数のチップレットを載せて相互接続するための中間層で、シリコンなどでできた配線専用の基板のことです。インターポーザの性能が高いほど、多くのチップレットを高密度に配置できて電気信号のやりとりがスムーズになります。

先進的なチップレット集積技術は、電力を効率的に供給する点においても重要な役割を果たします。チップをつなぐ部分に小さな金属製の接続点を多数設けることで、狭いスペースでも十分な数の接続経路を確保でき、データの高速伝送とスペースの有効利用が可能になります。

チップレットをさらに進化させる3D実装

現在のチップレット集積は、複数のダイをパッケージ内にまとめる「2.5次元(2.5D)実装」が主流ですが、次のステップとして「3D実装」と呼ばれる垂直方向の積層技術が注目を集めています。2.5D構造は、インターポーザにダイを横に並べることで高密度接続を実現してきました。これに対して3D実装は、TSV(シリコン貫通電極)などを用いてチップを垂直方向に積み重ねることで、さらなる高集積化を可能にします。

チップレットがもたらす柔軟な機能分割や異種回路統合に3D実装を組み合わせることで、性能の向上、省スペース化、省電力化に貢献します。データを保存する回路と計算処理を行う回路を垂直に重ねて配置することで大量のデータに高速にアクセスできるようになり、AIなどの高度な処理を短時間で実行可能になります。

一方、垂直に積み上げるため熱が集中しやすく、熱管理や歩留まり維持といった新たな課題に取り組む必要があります。こうした課題の解決に向けて先端パッケージング技術の研究が世界各国で活発化しており、チップレット×3D実装による次世代半導体の実現はムーアの法則に代わる大きなイノベーションと見なされています。

Rapidusのチップレットへの取り組み

Rapidusは、NEDO(新エネルギー・産業技術総合開発機構)のプロジェクトにおいて2nm世代の先端半導体製造技術を開発しており、その一環としてチップレット技術を活用した先端パッケージングに取り組んでいます。従来のシリコンインターポーザは大型化に伴うコスト高が課題となり得るため、Rapidusは有機材料を用いた再配線層(RDL)インターポーザやガラスキャリアなど、新たな素材や技術を使ってより大きいサイズのインターポーザを効率良く製造できる大判パネル方式に注目しています。

丸いシリコンウェーハと異なり、大判の四角形パネルを用いれば複数の基板を無駄なく切り出せるため、量産性の向上とコスト低減が期待できます。

ガラスキャリアは平たん性や絶縁性、熱膨張係数の制御といった特長があり、高周波回路の損失低減にも寄与します。また、チップレットによる多機能化、高性能化と併せて相乗効果を生む可能性もあります。大型パネルの加工や信頼性の確保など、乗り越えるべき技術的なハードルの解決に向けて研究開発を進めています。

チップレットと新たな材料や大判パネル技術を組み合わせることで、ムーアの法則の先を見据えた高性能かつ多機能の半導体製造を実現し、国内外の半導体産業に対して新たな価値を提供していきます。

シリコン基板に小さな穴を設けて導電性の材料を詰めること。上下に積み重ねたチップ間で高速かつ効率的に電気信号を伝送する技術。

- #半導体

- #後工程

- #チップレット

- #パッケージ