テクノロジー

枚葉式とは?

Rapidusが目指す「完全枚葉式」の半導体製造

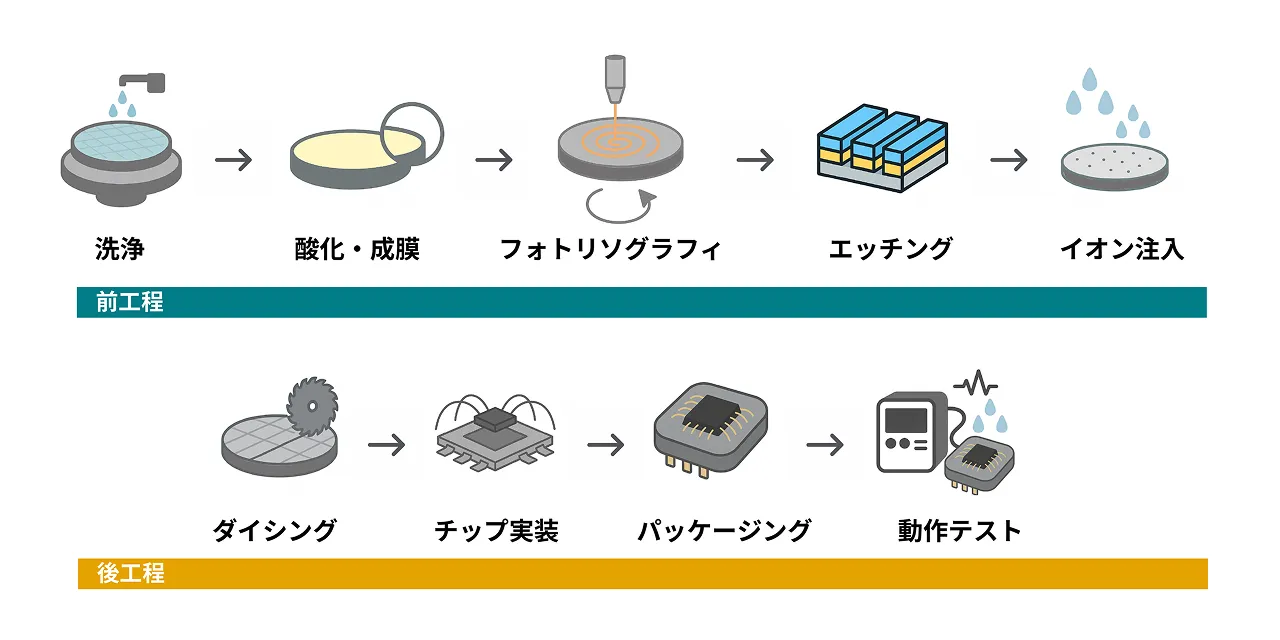

半導体はスマートフォンやPC、自動車など多様な分野で活躍する重要な部品です。その製造工程には多くのステップがあり、大まかに「前工程」と「後工程」に分かれます。

「前工程」と「後工程」に分かれる半導体の製造工程

半導体製造の前工程は、シリコンウェーハ上にトランジスタや配線などの微細な回路パターンを形成する工程です。シリコンウェーハとは、Si(シリコン)の結晶、いわゆるインゴットをスライスしたものです。ウェーハの口径が大きいほど多くの半導体を製造できるため、半導体業界は大口径化を進めており、最先端の半導体工場は300mm(12インチ)ウェーハを採用しています。このため全ての製造装置が300mmウェーハ対応の装置となります。

ウェーハの洗浄から始まり、酸化・成膜、フォトリソグラフィ(レジスト塗布、露光、現像)、エッチング、イオン注入、金属や絶縁膜の成膜、平坦化など多岐にわたる作業を数十回繰り返して多層配線を作り込みます。前工程では同じウェーハに対してこれらの処理サイクルを繰り返し、IC(集積回路)の素子および配線構造を構築していきます。

続く後工程とは、前工程で回路形成が完了したウェーハから個々のチップ(ダイ)を切り出し、パッケージ基板に実装して外部端子と接続し、最終的な半導体製品に仕上げる工程です。ダイシング(切り出し)、ダイボンドやワイヤボンド/バンプ接合によるチップの実装、モールド樹脂封止などのパッケージング、そして電気的な動作テストが含まれます。

後工程はOSAT(Outsourced Semiconductor Assembly and Test:後工程を専門とする企業)などに委託されることが多く、前工程を担当するファウンドリーと分業体制になっているのが一般的です。つまり現在の半導体産業は、設計、前工程、後工程がそれぞれ別主体で行われる分業モデルが主流となっています。近年はAI半導体のように高性能なCPUやGPUを広帯域のメモリーと組み合わせるニーズが急増しています。これには、完成したチップをパッケージの中で広帯域かつ短距離で接続したり積層したりして性能と消費電力の要求を満たす「チップレット」の導入が進んでいます。

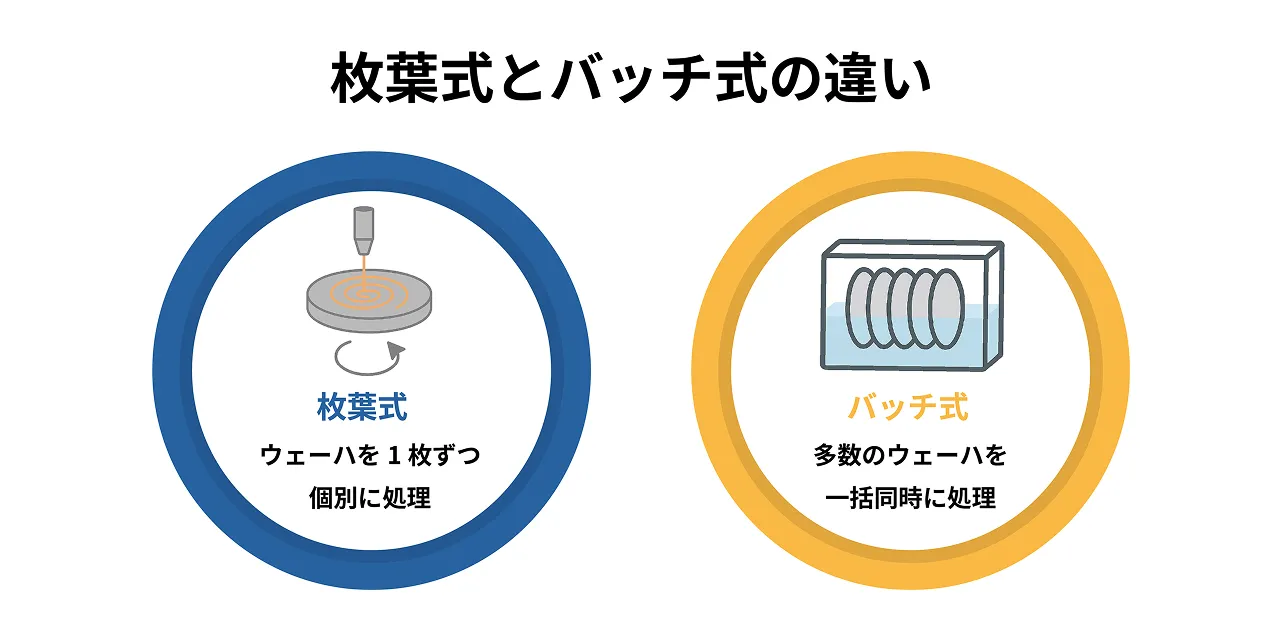

枚葉式とバッチ式の違い

前工程の製造装置には、ウェーハを1枚ずつ個別に処理する「枚葉式」と複数枚のウェーハをまとめて同時に処理する「バッチ式」の2方式があります。

枚葉式:ウェーハを1枚ずつ処理

ウェーハを1枚ずつ処理する枚葉式装置は、各ウェーハに対して細かなプロセス制御が可能であり、高い精度と均一性をもって処理できる点が大きなメリットです。微細加工や高性能が要求されるデバイス(高解像度CMOSイメージセンサーや先端CPUなど)の製造に適しており、スマートフォンやAI半導体、自動運転車向け半導体など繊細なプロセスを要する製品では枚葉式が多く採用されています。

枚葉式の利点は、ウェーハ間のばらつきが抑えられ高い歩留まりを実現しやすいことです。処理中のセンサーデータなどを詳細に取得・蓄積できるため、AI制御やフィードバックによってプロセスを最適化する取り組みにも適しています。

一方、ウェーハを1枚ずつ順番に処理する方式であるが故に、バッチ式と比べてスループットが低く大量生産には不向きです。高精度の制御が要求されるため装置自体が高価になり、必要な台数も増えることから一般的には量産時のコスト効率が悪化します。

バッチ式:一度に多数のウェーハを処理

バッチ式装置では薬液槽や加熱炉などに一度に多数(時には数十枚)のウェーハをまとめて投入して同時に処理します。この方式は、一括処理による高い生産効率とコスト効率があり、大量生産に適しています。メモリーチップや標準ロジックICなど数量が求められる製品では、バッチ式が用いられてきました。

バッチ式は一度に多くのウェーハを処理することで単位コストを削減でき、装置の導入費用も多くのウェーハで分散可能です。広く使われてきた成熟技術でもあり、安定性があります。

デメリットとして、複数のウェーハをまとめて処理するためにウェーハ間の微妙なプロセスサイズの差異から品質のばらつきが生じやすい点が挙げられます。また、一括処理のためにプロセス条件の変更や微調整が難しく、少量生産や頻繁な工程の切り替えに対応しにくい傾向があります。工程にもよりますが、ウェーハの入れ替えや温度の昇降には非常に長い時間がかかります。

| 項目 | 枚葉式 | バッチ式 |

|---|---|---|

| 処理方式 | ウェーハを1枚ずつ個別に処理 | 複数のウェーハを同時に処理 |

| 生産効率 | 低い(逐次処理のため時間を要する) | 非常に高い(一括処理で時間短縮) |

| 一枚当たりのコスト効率 | 高(装置投資・運用費が大きい) | 低(大量処理で費用分散) |

| 品質、均一性 | 高い精度、高均一(各枚を精密制御) | 均一性に制約(ウェーハ間で条件差が生じ得る) |

| 適した用途 | 微細加工や高性能が要求される高付加価値製品 | 大量生産品(メモリーや標準ロジックなど) |

| 柔軟性(条件変更など) | 高い(製品ごとに条件最適化が容易) | 低い(条件変更や小ロット対応は困難) |

表1:半導体製造における枚葉式とバッチ式の比較

枚葉式が近年重視されている理由

近年、枚葉式へのシフトが加速しています。背景には技術的要請と市場動向があります。

技術面では、半導体の線幅微細化や3次元構造化が進展し、プロセス条件の許容誤差が極めて小さくなっています。そのため従来以上にプロセス均一性と制御精度が重要となり、精密な枚葉式処理が不可欠になりつつあります。実際、300mmウェーハ世代の登場以降、多くの工程(洗浄やアニールなど)がバッチ式から枚葉式装置に置き換わってきました。洗浄では数十枚のウェーハを薬液槽に浸すバッチ式が一般的でしたが、300mm化以降は1枚ずつ薬液スプレーなどで精密洗浄する枚葉式装置の採用が進んでいます。

同時に半導体市場のニーズが多様化しており、一種類の汎用(はんよう)チップを大量生産するだけでなく、用途ごとに最適化されたカスタムチップを短期間で提供することが求められています。枚葉式はプロセスの変更や製造ロットの柔軟な切り替えが容易であるという利点があるため、ファウンドリー各社も小ロット試作から量産まで機動的に対応するために枚葉式ウェーハ処理装置を増やす傾向があります。

Rapidusが目指す完全枚葉式プロセスとは

Rapidusが掲げる技術戦略の柱の一つに、前工程の「全工程枚葉化」すなわち完全枚葉式プロセスラインの実現があります。Rapidusは「従来25枚1バッチで行ってきた処理を、全て1枚ずつ処理する枚葉式で行う」ことを掲げており、前工程に関わる全ての製造装置は枚葉式となります。

これは一部のファウンドリーに残っているバッチ式の熱処理工程(酸化、拡散、アニールなど)や洗浄装置などを含め、例外なくウェーハ1枚単位の処理に置き換える挑戦的な試みと言えます。

最先端の製造ラインには通常、数百ステップの工程があります。Rapidusが計画する2nm世代など最先端の技術ノードで新しい製品を完成させるには、設計を含めると年単位の時間がかかると言われています。

Rapidusは完全枚葉化によって各ウェーハから得られる膨大なプロセスデータを余すところなく収集、解析し、設計工程のフィードバックや製造の高精度化、歩留まりの向上につなげて「MFD」(Manufacturing For Design:設計のための製造)という概念を具現化する考えです。その結果、設計から製品化までの時間の大幅な短縮が可能となります。

また、完全枚葉式のメリットとして多品種専用チップの生産に柔軟に対応できる点があります。大量生産に加えて顧客ごとのカスタム仕様チップを短期間で提供するには、生産ラインの柔軟性が鍵となります。Rapidusは、イチから最新鋭ラインを構築する強みを生かして初期段階からフル枚葉、フル自動化、最新センサー活用を前提に設計することで、従来にはない俊敏な生産体制を目指しています。

こうした完全枚葉式による高精度かつ柔軟な生産体制は、Rapidusが掲げる新たなビジネスモデルへとつながります。RUMS(Rapid and Unified Manufacturing Service)では、前工程から後工程まで一貫して提供し、設計プロセスとの密接な連携を可能にします。

半導体製造の基盤となる薄い円盤状の材料のことを指します。シリコンなどを使用して作られています。ウェーハの上に回路やトランジスタが作り込まれ、最終的に半導体チップやプロセッサが製造されます。

Rapid and Unified Manufacturing Service の略。Rapidusが構築を目指すビジネスモデルのこと。設計支援と前工程、後工程を一貫して行い、顧客の要望に沿った2nm GAAプロセスを採用した最先端の専用チップやチップレットを、速いサイクルタイムで顧客に届けることを目標としています。

- #半導体

- #前工程

- #枚葉式

- #ウェーハ