テクノロジー

半導体前工程を解説 ナノスケール製造ステップの全体像

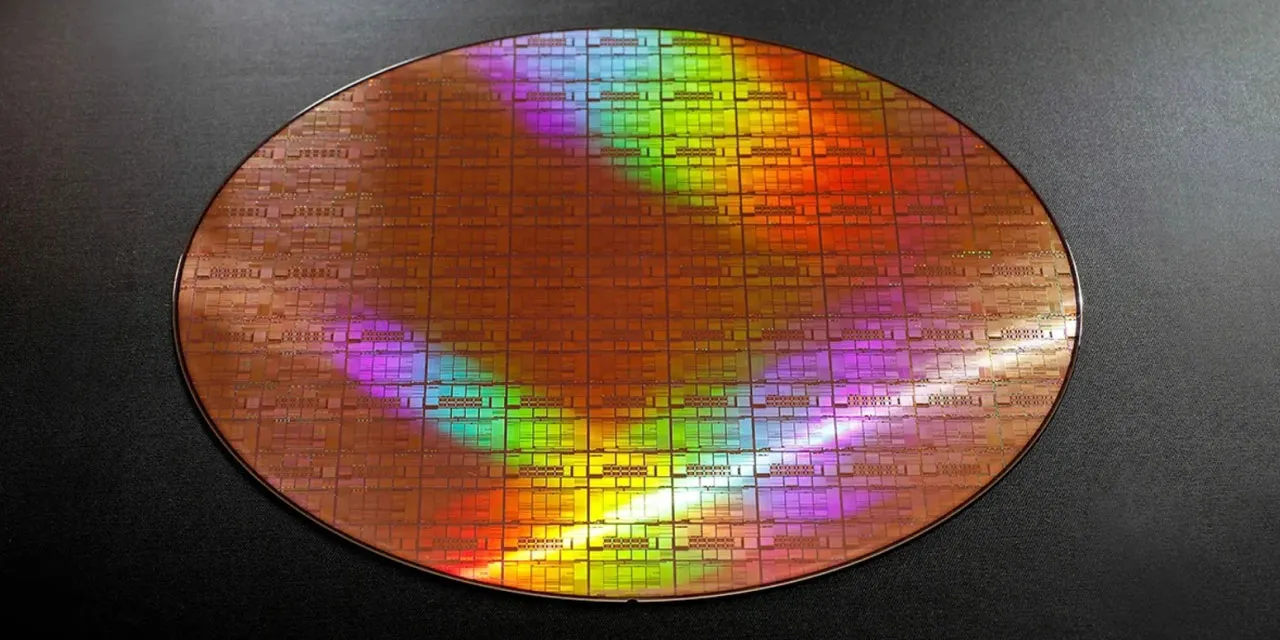

スマートフォンや家電、自動車、さらにはクラウド上のAIサーバまで、私たちの生活を支える製品には欠かせないのが半導体チップです。ナノメートル級の回路を描くには、ほこり一つも許されないクリーンルームという特別な環境が必要です。本記事ではシリコンウェーハ上にナノメートルスケール(1ナノメートル=10億分の1メートル)の回路を作り込む「前工程」に焦点を当て、その主な流れを解説します。

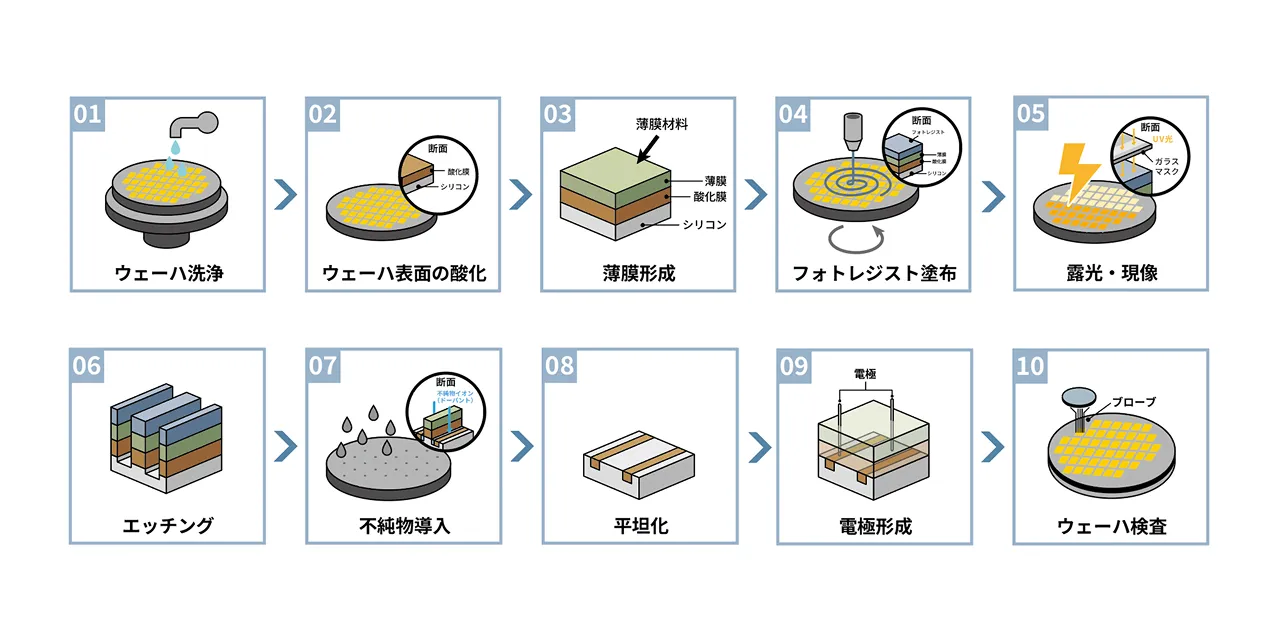

半導体前工程の全体像

半導体製造は、前工程と後工程に分かれます。前工程でウェーハ上にナノメートル級の回路を形成し、後工程でチップを切り出してパッケージ化します。

前工程では主に洗浄、酸化や拡散、CVDやスパッタリングなどによる成膜、フォトリソグラフィ、エッチング、イオン注入、平坦化、電極形成、ウェーハ検査といった一連のプロセスを繰り返し実施します。それぞれの工程において、非常に高い加工精度が求められ、最終的な半導体チップの性能や信頼性、製品の良品率である歩留まりに大きく影響します。

前工程の主要プロセス

ウェーハ洗浄

半導体における微細加工では、ナノレベルの金属不純物や有機物などの微小な汚染物質がデバイス不良の原因となってしまいます。そのため、超高純度な化学溶液による洗浄と超純水によるリンス(すすぎ)、そして乾燥によってウェーハ表面を常に清浄に保ちます。

代表的な洗浄方法に「RCA洗浄」と呼ばれるプロセスがあり、酸やアルカリの溶液を用いて有機物や金属汚染を除去します。洗浄は各工程の前後などさまざまな場面で繰り返し実施され、数百工程にも及ぶ前工程のおよそ3割を占めるとされています。洗浄ではナノレベルの微粒子まで除去する徹底ぶりです。

ウェーハの酸化、拡散

900~1100 度程の高温の拡散炉でウェーハ表面を酸素雰囲気にさらして均一なシリコン酸化膜(SiO₂)を形成します。この酸化膜は化学的に安定で、ウェーハ表面を保護するとともにトランジスタのゲート酸化膜として機能する重要な絶縁層です。近年ではRTP(Rapid Thermal Process)と呼ばれるウェーハを1枚ずつ短時間で高温に加熱して精密に温度制御する工程が使われています。そうすることで不純物活性化や結晶欠陥修復などを緻密かつ均一に処理できます。

薄膜形成

ウェーハ表面に絶縁膜、金属膜、半導体膜を成膜する工程です。

代表的な成膜手法には、化学反応を利用する「CVD」(Chemical Vapor Deposition)と物理的な手段を用いる「PVD」(Physical Vapor Deposition)の2種類があります。

- CVD:化学反応を利用して薄膜を成長させる技術で、熱CVDやプラズマCVD、さらに制御性に優れた原子層堆積(ALD:Atomic Layer Deposition)などがあります。

- PVD:主にスパッタリング法が用いられ、プラズマから発生したイオンをターゲット材料にぶつけて原子をはじき出し、ウェーハに堆積させる方法です。

フォトレジスト塗布

フォトリソグラフィ工程に入る前に、ウェーハ全面にフォトレジストと呼ばれる感光性の樹脂を塗布します。フォトレジストはスピンコーターと呼ばれる塗布装置によって薄く均一にコーティングされ、これによりウェーハ表面が光に反応する感光材料で覆われます。

フォトレジストは、後の露光で照射される紫外線などの光によって化学的性質が変化して露光後の現像によってパターン形成に寄与する重要な材料です。塗布後はレジストを安定化させるためにベーク(加熱処理)が行われ、次の露光工程に備えます。

露光・現像(フォトマスクを使ったパターン転写)

フォトレジスト塗布後、回路パターンを描いたフォトマスク(レチクルとも呼ばれる原版)と高解像度レンズを用いて、ウェーハ上に微細パターンを転写する露光を行います。露光装置はウェーハに光を照射し、フォトマスクのパターンをレジストに焼き付けます。露光に使用される光源は、その波長によって分類されており、UVランプのg線やi線、KrFやArFエキシマレーザー、そして現在最先端のEUV(極紫外線)などが活用されています。

光が当たった部分のレジストは化学反応により変化し、現像液にウェーハを浸す現像工程で照射部分のレジストが溶解・除去されます。これによってウェーハ表面にはレジストで保護された部分と露出した部分とがパターン状に残ります。

これがフォトリソグラフィの一連の流れです。現像後、レジストが残った部分が回路パターンのマスク(保護膜)となり、次のエッチング工程へ進みます。

エッチング(不要部分の除去)

エッチングでは、露光・現像によってパターン状に保護されたレジスト膜をマスクとして、レジストで覆われていない不要部分の薄膜や酸化膜を除去します。

エッチングには大きく分けてウェットエッチング(薬液による化学的溶解)とドライエッチング(プラズマ中で化学反応と加速したイオンによる薄膜除去)の2種類があります。シリコン酸化膜はフッ酸系薬液で溶解除去し、金属膜は塩素系ガスプラズマでイオンを衝突させて削り取ります。

エッチングが進むと、下地のシリコン基板や前工程で形成した層がパターン通りに露出し、不要な部分の材料だけが除去されます。エッチング後には残っているレジスト自体も不要となるため、薬品によってレジストを剥離し、洗浄して清浄な表面を露出させます。

不純物導入

エッチングによって所定のパターンが開口、形成された後、その目的に応じてさまざまな追加プロセスを施します。トランジスタの電極・ドレイン領域を形成する場合には、開口部からシリコン基板中に不純物(ドーパント)を導入します。導入方法は「拡散」と「イオン注入」の2つが代表的です。

- 不純物拡散法:高温下でウェーハを不純物ガスにさらし、シリコン中にボロンやリンなどの不純物原子を熱拡散させます。

- イオン注入:不純物原子をイオン化して加速し、狙った深さと濃度でシリコン基板に打ち込みます。

これらの不純物導入工程によって、シリコンに電気的性質(N型やP型の伝導特性)を持つ領域が作り込まれ、半導体デバイスの基本動作が可能になります。

平坦化(CMP)

複数回にわたる成膜とエッチングを経ていくうちに、ウェーハ表面には凹凸が生じていきます。この表面凹凸によって、次に塗布するフォトレジストが均一な膜厚にならず、露光時の精度にも悪影響を及ぼします。また、多層配線の積層プロセスにおいて、上層の形成に支障が出ないようにするために絶縁膜や配線層の平坦化が不可欠となっています。

そこで各層の形成後などに行われるのが平坦化プロセスです。代表的な手法はCMP(化学機械研磨)と呼ばれ、研磨剤を含むスラリー(化学薬品液)と研磨パッドを用いてウェーハ表面を物理的かつ化学的に磨いて凹凸を除去します。CMP工程によりウェーハ表面は鏡面のように平坦化され、再びフォトリソグラフィ工程に適した状態に戻ります。

ここまでの工程(洗浄、成膜、フォトレジスト塗布~平坦化)を何度も繰り返すことで、ウェーハ上にトランジスタや配線層などの多層構造を少しずつ構築していきます。

電極形成

前工程の最後に電気的な接続のために外部との接点となる電極パッドを形成します。典型的にはアルミニウムなどの金属膜をウェーハ全面にスパッタリング法を使って成膜し、再度フォトリソグラフィとエッチングで配線パターンを形成します。配線層には銅(Cu)が使用されています。Cu配線では絶縁膜の溝にCuを電解めっきで埋め込み、不要な部分を研磨で除去するダマシン法と呼ばれる工程が使われています。 こうして形成された電極は、チップ外部との電気的な経路となります。電極形成後には、最終仕上げとして表面を保護するパッシベーション膜(保護膜)を形成し、チップを保護します。

ウェーハ検査(プローブテスト)

ウェーハ検査では完成したシリコンウェーハ上の複数のチップそれぞれが電気的に正常動作するかを検査します。これをウェーハプロービング(またはプローブテスト)と呼び、ウェーハ上の各チップの電極パッドに細い針(プローブ)を接触させて電気的にテストを行います。

テストではチップの基本的な動作確認や電気特性の測定が高速に実施され、不良と判定されたチップにはインクマークを付ける、または座標を記録します。この段階でウェーハ上の良品、不良品の識別がなされて歩留まりも把握されます。

まとめ

以上が半導体チップ製造の前工程における主な流れです。シリコンウェーハ上に酸化膜を形成し、レジスト塗布・露光・エッチングによる微細パターン形成、不純物の導入、層間絶縁膜などの成膜、平坦化、金属配線形成、そしてウェーハ単位の検査に至るまで、多岐にわたる高度な工程を経て一枚のウェーハが完成します。

前工程で作り込まれたウェーハはこの後、後工程と呼ばれるチップの切り出しからパッケージ化までの工程へと引き継がれます。前工程が半導体の機能を形成する要であるのに対し、後工程は完成品としての形を与える重要なステージです。次回の記事では、後工程についてさらに詳しく紹介していきます。

- #半導体

- #前工程

- #ウェーハ

- #枚葉式

- #歩留まり