Technology

Semiconductor Front-End Processing: An Overview of Nanoscale Manufacturing Steps

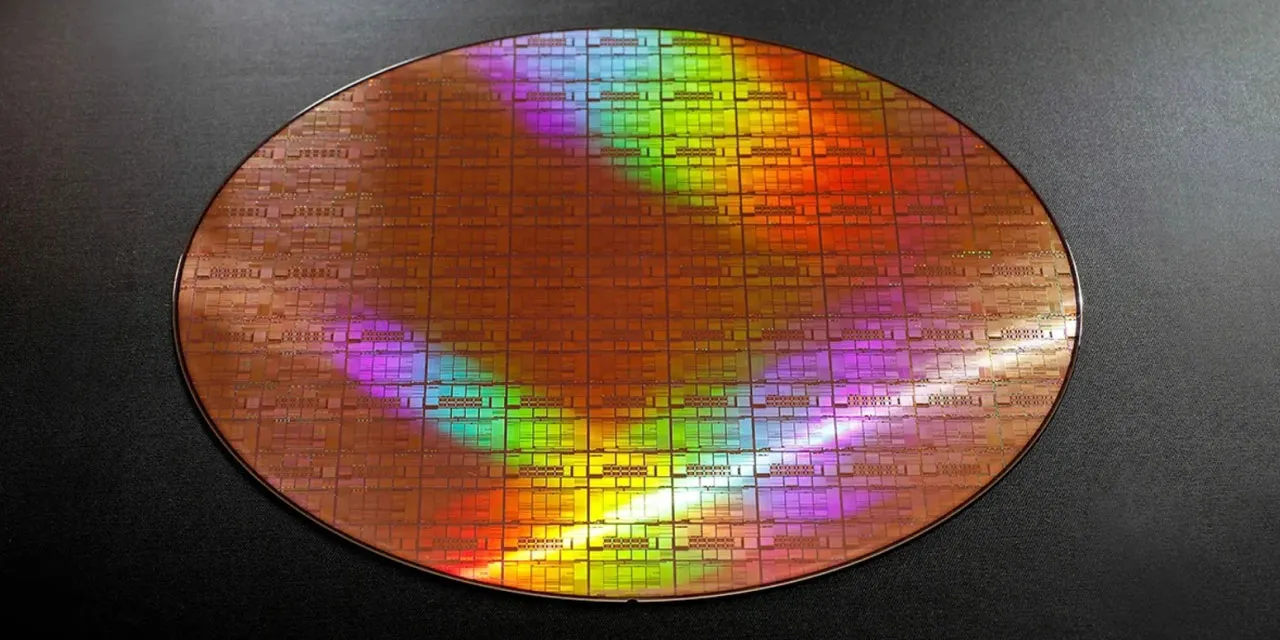

Semiconductor chips are essential components in the products that support our daily lives—from smartphones and home appliances to automobiles and AI servers in the cloud. Creating circuits at the nanometer (nm) scale requires a specially controlled environment called a cleanroom, where not even a single speck of dust is allowed. This article focuses on the front-end process of building nanometer-scale circuits (1 nm = one-billionth of a meter) on silicon wafers and explains the main workflow.

A Snapshot of the Semiconductor Front-End Process

Semiconductor manufacturing is divided into front-end and back-end processes. In the front-end process, nanometer-scale circuits are formed on wafers, while in the back-end process, chips are cut out and packaged. The front-end process primarily involves repeating a series of steps including cleaning, oxidation and diffusion, film formation through CVD and sputtering, photolithography, etching, ion implantation, planarization, electrode formation and wafer inspection. Each process requires extremely high precision and significantly affects the final chip's performance, reliability and yield—the percentage of good products.

Major Front-End Processes

Wafer Cleaning

In semiconductor microfabrication, nanoscale contaminants such as metallic impurities and organic substances can cause device failures. Therefore, wafer surfaces are constantly kept clean through cleaning with ultra-high-purity chemical solutions, rinsing with ultrapure water and drying.

An example cleaning method is the RCA cleaning process, which uses acid and alkaline solutions to remove organic matter and metallic contamination. Cleaning is repeated at many stages, accounting for roughly 30% of all processing steps in the front-end process, which can total several hundred steps. The cleaning is so thorough that it removes particles down to the nanoscale level.

Wafer Oxidation and Diffusion

The wafer surface is exposed to an oxygen atmosphere in a diffusion furnace at high temperatures of around 900–1100°C to form a uniform silicon oxide film (SiO₂). This oxide film is chemically stable and serves as an important insulating layer that protects the wafer surface and functions as the gate oxide film in transistors.

In recent years, a process called rapid thermal process (RTP) has been used, which heats wafers one at a time to high temperatures for short periods with precise temperature control. This enables precisely controlled and uniform processing for impurity activation and crystal defect repair.

Thin Film Formation

This is the process of depositing insulating, metal and semiconductor films on the wafer surface. There are two types of film formation techniques—chemical vapor deposition (CVD), which uses chemical reactions, and physical vapor deposition (PVD), which uses physical means.

- CVD: A technology that grows thin films using chemical reactions, including thermal CVD, plasma CVD and atomic layer deposition (ALD), which offers superior control.

- PVD: Mainly uses the sputtering method, where ions generated from plasma collide with the target material, knocking out atoms that are then deposited on the wafer.

Photoresist Application

Before entering the photolithography process, a photosensitive resin called photoresist is applied to the entire wafer surface. The photoresist is thinly and uniformly coated by a device called a spin coater, covering the wafer surface with a photosensitive material that reacts to light.

Photoresist is a key material that changes its chemical properties when exposed to ultraviolet or other light during subsequent exposure, contributing to pattern formation through development after exposure. After application, the resist is heat-treated to stabilize it in preparation for the next exposure process.

Exposure and Development—Pattern Transfer Using Photomasks

After photoresist application, exposure is performed to transfer fine patterns onto the wafer using a photomask, also called a reticle, which is the master template, with circuit patterns drawn on it and high-resolution lenses. The exposure equipment irradiates light onto the wafer, imprinting the photomask pattern onto the resist.

The light sources used for exposure are classified by wavelength, including UV lamp g-line and i-line, KrF and ArF excimer lasers, in addition to the most advanced extreme ultraviolet (EUV) approaches.

The resist in areas exposed to light changes through chemical reactions, and in the development process where the wafer is immersed in developer solution, the resist in the exposed areas dissolves and is removed. This leaves a pattern on the wafer surface with areas protected by resist and exposed areas.

This is the complete flow of photolithography. After development, the areas where resist remains become the mask or protective film for the circuit pattern, and the process moves to the next etching step.

Etching—Removal of Unnecessary Parts

Using the resist film protected in a pattern through exposure and development as a mask, unnecessary thin films and oxide films not covered by resist are removed.

Etching is broadly divided into two types: wet etching or chemical dissolution using chemicals and dry etching, thin film removal in plasma through chemical reactions and accelerated ions. Silicon oxide films are dissolved and removed with hydrofluoric acid-based chemicals, while metal films are scraped away by colliding ions using chlorine-based gas plasma.

As etching progresses, the underlying silicon substrate or layers formed in previous processes are exposed according to the pattern, and only unnecessary materials are removed. After etching, the remaining resist itself becomes unnecessary, so the resist is stripped using chemicals and cleaned to expose a clean surface.

Impurity Introduction

After the designated pattern has been opened and formed through etching, various additional processes are applied according to the purpose. When forming the source and drain regions of transistors, impurities or dopants are introduced into the silicon substrate through the openings. Two introduction methods include diffusion and ion implantation:

- Impurity diffusion method: The wafer is exposed to impurity gas at high temperatures, thermally diffusing impurity atoms such as boron or phosphorus into the silicon.

- Ion implantation: Impurity atoms are ionized and accelerated, then implanted into the silicon substrate at the targeted depth and concentration. Through these impurity introduction processes, regions with electrical properties, N-type or P-type conduction characteristics, are created in the silicon, enabling the basic operation of semiconductor devices.

Planarization

As multiple rounds of film formation and etching are performed, irregularities develop on the wafer surface. These surface irregularities prevent the next photoresist application from achieving uniform film thickness and adversely affect exposure precision. Additionally, in the multilayer wiring stacking process, planarization of insulating films and wiring layers is essential to ensure the upper layer formation proceeds without problems.

Therefore, a planarization process is performed after forming each layer. The representative technique is called chemical mechanical polishing (CMP), which physically and chemically polishes the wafer surface using a slurry of chemical liquid containing abrasives and a polishing pad to remove irregularities.

The CMP process planarizes the wafer surface to a mirror-like finish, thus restoring the wafer surface to a condition suitable for the next photolithography cycle.

By repeating the processes up to this point of cleaning, film formation, photoresist application through planarization, many times, multilayer structures such as transistors and wiring layers are gradually built up on the wafer.

Electrode Formation

At the end of the front-end process, electrode pads are formed as contact points with the outside for electrical connections. Typically, a metal film such as aluminum is deposited on the entire wafer surface using the sputtering method, and wiring patterns are formed again through photolithography and etching.

Copper (Cu) is used for wiring layers. For Cu wiring, a process called the damascene method is used, in which Cu is first electroplated into the grooves of the insulating film and then the excess metal is removed by polishing.

The electrodes formed in this way become the electrical pathways to the outside of the chip. After electrode formation, a passivation and protective film is formed as a final finish to protect the surface and safeguard the chip.

Wafer Inspection

In wafer inspection, each of the multiple chips on the completed silicon wafer is tested to verify that they can operate normally electrically. This is called wafer probing or probe testing, where thin needles called probes are brought into contact with the electrode pads of each chip on the wafer to perform electrical testing.

During testing, basic operational checks and electrical characteristic measurements of the chips are performed at high speed, and chips identified as defective are marked with ink or their coordinates are recorded. At this stage, good and defective products on the wafer are identified and the yield is also determined.

Summary

The above describes the main workflow in the front-end process of semiconductor manufacturing. A single-wafer process is completed through numerous intricate and highly sophisticated processes—from forming oxide films on silicon wafers, fine pattern formation through resist application, exposure and etching, impurity introduction, film formation of interlayer insulating films, planarization and metal wiring formation, to wafer-level inspection.

The wafer fabricated in the front-end process is then handed over to the back-end process, spanning chip dicing to packaging. While the front-end process is the core that forms the functions of semiconductors, the back-end process is an important stage that gives form to the finished product. The next article will introduce the back-end process in more detail.

- #Semiconductor

- #Front-End

- #Wafer

- #Single-Wafer Process

- #Yield